GigaDevice GDP1BFLM-CB CXMT G3 2Gb DDR3L SDRAM Transistor Characterization

Share This Post

This report presents Key DC characteristics for NMOS and PMOS transistors located in the word line drivers and sense amplifiers regions of the GigaDeviceHUANGSHAN4G die found inside the GDP1BFLM DDR3L SDRAM component extracted from a MiliankeMLK-CA03FPGA development board.

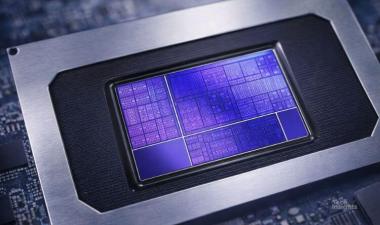

The MiliankeMLK-CA03 is a field programmable gate arrays (FPGA) development board containing two of the GigaDeviceGDP1BFLM BGA packages. The GDP1BFLM BGA package measures 13.00 mm ×7.50 mm ×0.94 mm thick and has 96 solder balls. The GDP1BFLM package contains a single 2 Gb CXMT G3 DDR3L SDRAM die. The DDR3L SDRAM (HUANGSHAN4G) die measures 6.26 mm × 6.31 mm (39.50 mm2) as measured from the die seals or 6.30 mm ×6.36 mm (40.07 mm2) for the full die. The die was manufactured using a DRAM CMOS process incorporating four back-end of line (BEOL) interconnect layers, one tungsten (W), two copper (Cu), one aluminum (Al), with bit line (BL) under capacitors and a buried word line (WL) forming the gate of the buried cell array transistor (BCAT).

Electrical measurements of the word line drivers and sense amplifiers transistors for the HUANGSHAN4G die were performed in scanning electron microscopy (SEM) based environment using Kleindiek Nanotechnik probing system and a Keithley 4200A-SCS semiconductor characterization system. Transistors were measured at 85º C.