Agenda for Day One: Tuesday November 1, 2022

9:00 – 9:15 AM

9:15 – 10:00 AM

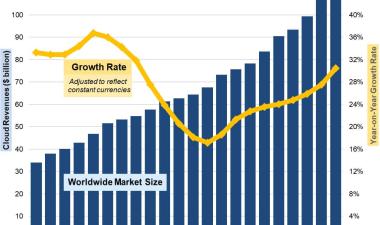

Keynote: Presentation: AI Moves From Cloud to Edge

Linley Gwennap, Principal Analyst, TechInsights

Linley Gwennap is a principal analyst of TechInsights and editor-in-chief of Microprocessor Report. One of the most respected analysts in the microprocessor industry, he has followed the industry for more than 20 years. Starting as a processor designer at Hewlett-Packard, Linley later worked in PA-RISC marketing and then became editor-in-chief of Microprocessor Report and vice president of MicroDesign Resources before founding The Linley Group in 1999. TechInsights acquired The Linley Group in 2021.

Hardware AI accelerators now appears in a wide range of processors including chips for servers, smartphones, vehicles, and a vast array of edge devices. By the end of next year, all new PC processors will feature AI hardware. New architectures and technologies, including photonic and analog computing, are emerging in the data center and at the edge. This presentation will review recent news and trends for AI accelerators of all types.

10:00 – 10:20 AM

BREAK – Sponsored by Flex Logix

10:20 AM – 12:25PM

Track A

Session 1: AI Accelerators for SoCs

SoC developers are increasingly integrating deep-learning accelerators (DLAs) into their chips. DLA IP makes it possible to do so without having to design custom DLAs. This session, led by TechInsights Senior Analyst Bryon Moyer, explores issues driving DLA-IP architectures, Transformer implementations, and a discussion on the benefits of off-the-shelf IP rather than a custom core. It includes a new IP-family announcement.

System-Level Advances in Neuromorphic Performance, Efficiency, Configurability, and Scalability

Anil Mankar, Chief Development Officer, BrainChip

Anil Mankar has spent 30 years developing products in the semiconductor industry. At Western Digital, Mr. Mankar developed PC core Logic chipsets. During his years at Conexant Systems Inc. in the position of VP of Engineering, he developed multiple products across industry segments and later became the company’s Chief Development Officer overseeing all product development for V92 Modem, DSL, Set-top boxes, PC audio and video ‘System on a Chip’ products. Mr. Mankar was SVP of VLSI Engineering at Mindspeed Technologies, responsible for Wireless and VOIP infrastructure product development.

Every real-world embedded AI application has a unique set of constraints on system latency, power, bandwidth and die size. Designing a single AI accelerator architecture to meet the needs of multiple applications is a major challenge. This presentation describes how BrainChip uses HW/SW co-design, AutoML, and the results of discussions with many AI application customers to achieve advances in system-level hardware performance, efficiency, configurability, and scalability with its neuromorphic compute architecture.

Thinking of Designing your Own NPU? Perhaps You Should Reconsider

Sharad Chole, Chief Scientist, Expedera

Sharad Chole is the chief scientist and a co-founder at Expedera. He brings extensive experience in software-hardware co-development to enable efficient AI processing. Sharad is an expert in AI frameworks, power-aware neural network optimizations, DNN, and programmable dataflow architectures. Previously, he was an architect at Cisco, Memoir Systems (Cisco), and Microsoft. He holds a BS from IIT Kanpur.

A relatively new class of processor, the NPU (Neural Processing Unit), is taking its place in heterogeneous designs. As a result, chip designers who rarely consider creating custom CPU or GPU architectures are grappling with whether to design their own custom NPUs. This talk will highlight the complexities of designing NPUs and explore why a better option might be a silicon-proven, packet-based AI engine that allows you to customize for current and future workloads.

Building Vision Inference Systems Using Transformer Models

Cheng C. Wang, CTO, Flex Logix

Cheng Wang, co-founder and CTO of Flex Logix. He has invented and developed many key technologies in both eFPGA and inference product lines, spanning architecture, silicon, and software. He holds a B.S. in EECS from UC Berkeley, and M.S. & distinguished Ph.D. from UCLA. He's received the Lewis Winner Award for Outstanding Paper at ISSCC 2014, and holds multiple patents on eFPGA and neural inferencing.

Transformer AI models have become the de-facto standard for natural language processing (NLP). With great NLP results, researchers looked at applying transformers to vision and created a network called the Vision Transformer (ViT), delivering a very high degree of accuracy over traditional vision models. Transformer models come with challenges for inference and edge-based systems due to the additional computation complexity and the underlying structure transformers. In this talk we will discuss how to architect solutions to implement transformers efficiently for the edge.

Introducing a Family of General-Purpose Neural-Processor IP

Nigel Drego is the CTO and Co-founder at Quadric. Nigel brings extensive experience in software and hardware design to his role at quadric. Nigel is an expert in computer architecture, compiler technology, and software frameworks. He was Chief Architect at 21.co, a company building and deploying Bitcoin mining technology. Previously he was a researcher at PDF Solutions and a designer at Intel. He holds a Ph.D. from MIT.

Ever expanding requirements for efficient ML inference capability have given rise to a new class of programmable processor for SoCs – the neural processor unit (NPU). Quadric’s GPNPU is a second-generation inference-optimized processor that is equally adept at running complex DSP C++ code and executing ML graphs, delivering optimal inference efficiency with less hardware-integration complexity and dramatically higher software developer productivity. This presentation will explore the innovations resulting in the architecture and software stack.

This session will include Q&A after each presentation.

Track B

Session 2: Novel Approaches to Safety, Security, Reliability, and Performance

As designers chase higher performance and greater functionality in areas ranging from automobiles to data centers, they must apply new technologies to ensure safety, security, reliability, and performance. This session led by TechInsights Director of Market Analysis Joseph Byrne looks at technologies for in-memory computing, safe virtualization, and reliable AI processing.

Delivering Reliable and Secure Performance Through Multithread Computing

Venkat Mattela, Founder and CEO, Ceremorphic

Venkat has over three decades of engineering and management experience in developing differentiated products and building successful businesses. Prior to founding Ceremorphic, he founded Redpine Signals, Inc., a wireless technology company that he sold to Silicon Labs, Inc. for $308M. Previously, Venkat held roles as Director of Engineering, Network Media Processors for Analog devices, and Director of Engineering, TriCore – MCU DSP for Infineon Technologies. He started his career at Tata Institute of Fundamental Research, India in January 1983. Venkat holds a PhD in Electrical Engineering from Indian Institute of Technology and is a graduate of Harvard Business School. Venkat has over 100 US and international patents.

Reliability and security are key to machine learning applications involving high-precision computing in real time with big data sets. Training workloads, which run for long times, make reliability and security paramount requirements. Conventional methods for high-performance computing, however, are prohibitively expensive for silicon size. Ceremorphic uses its patented multithread-processor architecture to solve the challenges of silicon area, fast recovery, and secure execution. This presentation covers Ceremorphic’s processing architecture for secure and reliable computing.

Using Software to Overcome Analog Loss for In-Memory Computing

Miao Hu, CTO & Co-founder, TetraMem

Miao Hu is CTO & Co-founder of TetraMem. Before that, he was an assistant professor at the ECE department of Binghamton University- SUNY from 2017 to 2020. He received the PhD degree in Electrical Engineering from University of Pittsburgh in 2014 and his master degree from Polytechnic Institute of NYU in 2011. He got his B.S. degree in Automation from Shanghai Jiao Tong University, China in 2008. Miao’s research focuses on RRAM, device and circuit modeling, in-memory computing and other von Neumann computing architecture like neuromorphic computing. He was ranked one of the world most influential scholars for AI technology by Aminer. He has published more than 40 journal/conference papers and 25 patents, with Google scholar citation over 8000.

Modern in-memory-computing solutions use an analog approach to gain throughput and energy efficiency over pure digital solutions. However, analog loss is the main concern; Building calibration circuits or re-training models is often unaffordable or unreliable. Here, TetraMem describes its software solution to overcome the analog loss by considering process and hardware variation, parasitic effects, nonlinearity, thermal stability, and other factors. The solution guarantees high flexibility, high reliability, and negligible software cost compared with retraining. It also has zero hardware overhead.

A Hardware Virtualisation Architecture for Safe Multi-ECU Controllers

Steve McAslan, Technical Director, NXP Semiconductors

Steve McAslan is a Technical Director with NXP Semiconductors. He has over 30 years’ experience developing, patenting and introducing new microprocessor technology to the automotive and other industries. Steve holds degrees in electronics and software engineering from Strathclyde and Heriot-Watt Universities and is an Honorary Lecturer at the University of Glasgow.

Modern software-defined vehicles require centralized controllers that can host multiple, independent functions. While solutions using software-supported virtualization are well-known, NXP has created an SoC architecture using flexible hardware which integrates virtualization and partitioning with safe fault-handling and security. This talk describes the implementation of the architecture on the S32Z/E real-time processors and shows how it can be used to build a multi-ECU environment with isolation from a line of code to a pin.

speedAI Architecture: The 2 PetaFlop, 30 TeraFlops/W At-Memory Inference Accelerator

Robert Beachler, VP of Product, Untether AI

Mr. Beachler has been involved in the creation of many market-leading silicon and software products in his career. During 16 years at Altera (now Intel PSG) he helped architect MAX 7000 CPLDs, Max+Plus II and Quartus design software. He led product definition at a series of groundbreaking startups in reconfigurable computing (Stretch, sold to Exar), neuromorphic computing (BrainChip), and analog computation (Analog Inference). He holds a BSEE from The Ohio State University.

Untether AI introduces speedAI240, its second-generation at-memory compute device specifically designed for the acceleration of neural networks. The speedAI family builds upon the first generation, runAI, with enhancements in energy efficiency, compute density, accuracy, scalability, and programming flexibility that are required for the variety of today’s neural-network architectures. This presentation will show the performance, energy consumption, and accuracy impacts of the intentional codesign of the new dual RISC-V memory bank with the new FP8p (precision) data type.

This session will include Q&A after each presentation.

12:25 – 1:55 PM

LUNCH Sponsored by Flex Logix

1:55 PM – 3:30 PM

Track A

Session 3: Application-Specific Processors

Although most processors are designed for large or general-purpose markets, some offer a specific set of features for a narrower set of workloads. To achieve optimal cost, power, and performance, these designs include domain-specific hardware accelerators while still offering programmability for customer-specific capabilities. This session, led by TechInsights principal analyst Linley Gwennap, presents three such designs: a DSP for radar processing, a DSP for 5G cellular basebands, and a DPU for network acceleration.

Tailored Automotive Radar Processing with DSPs

David Bell, Product Marketing Director for Tensilica CPU, DSP and AI Products, Cadence

David Bell, product marketing director for Tensilica CPU, DSP, and AI products at Cadence, has over 25 years of experience in the semiconductor industry. He joined Cadence after many years as an applications manager at Texas Instruments, supporting embedded Arm and DSP hardware and software products that serve industrial, automotive, communications, and other markets. Dave has been closely involved in the full SoC product development cycle from early specification through production in the final product.

Radar is one of several technologies that allow a car to “see” and track many objects both nearby and in its path, in a way that provides three-dimensional position as well as motion information. This presentation will discuss the ConnX DSP family and how it provides a system designer with the optimal compute capacity, precision, and dynamic range along with easy-to-use software libraries and tools to most efficiently implement a low-power solution that easily integrates into the processing subsystem.

5G RAN Baseband Platform IP for Cellular Infrastructure Solutions

Eric Cowden, Senior Field Application Engineer, CEVA

Eric is a Sr. Field Application Engineer at CEVA. With over 20 years of experience in the semiconductor industry, Eric’s background spans multiple technology areas including communications infrastructure, IoT, System-on-chip (SoC), advanced microprocessor and DSP architectures while working at companies including Motorola , Freescale, and MediaTek. He holds a B.Sc degree in Electrical Engineering from Northern Illinois University.

Modern 5G infrastructure devices require immense amount of compute to process vast amounts of channels and antennas. Significant baseband compute is required for both the DU and RU. This presentation will discuss new IP compute platforms with optimized HW/SW partitioning, including baseband vector DSPs and HW acceleration for all processing chains. The IP offers ASIC vendors comprehensive Layer 1 compute platforms for next-generation RU and DU devices, and it provides significant cost and power savings relative to COTS platforms.

DPUs: Where Will They Go Next?

Manoj Roge, Senior Director, Marvell Technology

Manoj has over 28 years of semiconductor and systems experience. He is responsible for business development and ecosystem partnerships for OCTEON DPU solutions. Previously, Manoj has held senior management and engineering positions at Achronix, Xilinx, Intel-PSG and Cypress Semiconductor. He successfully defined and executed new product strategies that resulted in significant increase in market share for the respective companies during his tenure. He has deep understanding of design requirements for broad set of market segments and fosters relationships with customers, ecosystem partners and standards bodies to deliver innovative solutions to market. He holds an MBA from Santa Clara University, MSEE from University of Texas, Arlington and BSEE from University of Mumbai. He holds 10 patents.

In a relatively brief period of time, DPUs have gone from being a concept to widely deployed across cloud infrastructures for offloading network, storage and security. These processors, which mix domain-specific hardware accelerators and performance/power-optimized Arm cores, will expand to accelerate entire applications such as 5G vRAN, firewall, load balancer or hosting complete infrastructure services in cloud and edge data centers. This presentation will discuss DPU use cases and technological shifts driving their growing influence and compelling TCO benefits.

This session will include Q&A after each presentation.

Track B

Session 4: System & FPGA IP

The stars of any new SoCs are typically the processing cores—CPUs, GPUs, and AI accelerators. But those components are supported by critical chip infrastructure that can make the difference between success and failure. This session, hosted by TechInsights Senior Analyst Bryon Moyer, looks at the role of networks-on-a-chip (NoCs) and clock networks in realizing a high-performance SoC. It also covers real-time hardware changes in embedded FPGAs (eFPGAs).

AI and NoCs Are Driving the Future of ADAS

Guillaume Boillet, Director of Product Management, Arteris IP , Carlos Román, Head of ASIC Solutions Architecture & Technical Sales, Sondrel, Inc.

Guillaume is Sr. Director of Product Management at Arteris where he drives the product lifecycle of the interconnect IP and IP deployment software portfolios. He has more than 20 years of combined experience in system-on-chip design, implementation, and verification from working in the mobile semiconductor and EDA industries. He holds two MSEEs from CentraleSupélec in Paris and École Polytechnique de Montréal and got his MBA from Grenoble Ecole de Management. He is a Certified Product Manager by the Pragmatic Institute.

Combined 30+ years of experience in Semiconductors, EDA tools, SoC Design, and Manufacturing Operations. Carlos held technical & managerial positions at Bell-Labs, AT&T Microelectronics, Cadence, and eSilicon Corporation. He joined Sondrel in October’2020 as Head of ASIC Solutions Architecture & Technical Sales with the purpose to expand Sondrel’s footprint in North America. Carlos holds an MSEE degree from Cornell University. His areas of specialization include Telecommunications Systems, ASIC Design & Manufacture, and Formal Verification tools.

Architecting for the future of ADAS requires a design edge to keep pace with today’s market pressures. Developers need expertise in systems, software, and specialized hardware algorithms. This talk discusses how the benefits of AI, computer vision and network-on-chip come together to accelerate entry into the next generation of automotive driver-assistance SoCs.

Reducing Chip and System Power for AI Solutions Through Intelligent Clock

Aakash Jani, Solutions Marketing Director, Movellus

Aakash Jani is the solutions marketing director at Movellus. Previously, he was a senior analyst at TechInsights/The Linley Group and a senior editor at Microprocessor Report. During his career, Aakash has served in processor design, verification, and validation roles at AMD and Intel on various chip designs, including standalone processors, graphics chips, and integrated SoCs. He holds a Bachelor of Science degree in Chemical Engineering from The University of Texas at Austin.

The explosion of cognitive AI models has led to larger and more complex silicon solutions. The increased complexity and die area come with a hefty price tag in the form of a high TDP rating, affecting the system, electricity, and emission costs for edge, automotive, and data center applications. This presentation investigates how intelligent clock networks help design teams reduce power by mitigating the adverse effects of workload changes, high switching activity, and silicon variation.

Using Software to Dynamically Reconfigure eFPGAs

Andy Jaros, VP IP Sales and Marketing, Flex Logix

Andy Jaros is responsible for Flex Logix’s EFLX and nnMAX IP. He has over 20 years of sales and sales management experience starting as Account Sales Manager at Motorola Semiconductor then Director Strategic Accounts at Arm. Moved to ARC as VP Sales, North America and continued ARC sales responsibilities when ARC was acquired by Virage and then Synopsys.

Today many ASIC, DPU, CPU and applications processors leverage companion FPGAs. By integrating eFPGA IP, software developers can use application specific accelerators to improve performance, maximize compute density, and dynamically change them via software as workloads change. Hardware acceleration can now be put in the hands of software developers allowing system companies to extend the lifecycle of their products, accelerate new features over time, and at the same time reduce cost and power.

This session will include Q&A after each presentation.

3:30 – 3:50 PM

BREAK Sponsored by Ceremorphic

3:50 – 5:25 PM

Track A

Session 5: Design

When discussion advanced new SoCs, the focus is often on the architecture and performance. But, underlying that, the silicon processes and design methodologies heavily impact the viability of those architectures. This session, led by TechInsights Senior Analyst Bryon Moyer, explores new ways of addressing reliability and measuring performance as well as how silicon photonics can enable quantum computing.

Increasing Data-Center Reliability by Predicting Defects and Monitoring Aging

Marc Hutner, Senior Director of Product Marketing, proteanTecs

Marc Hutner has been innovating in the areas of Design, Test, DFT and Data Analytics for more than 20 years. In October 2021, he joined proteanTecs where he is Sr. Director of Product Marketing enabling an advanced data analytics approach throughout your products life. Previously, he worked at Teradyne for more than 20 years as a silicon and system architect. A recognized thought leader for design and test at conferences, publications, podcasts and industry roadmaps. Marc has a Bachelor of Computer Engineering (B.Eng) from McGill University in Montreal Canada and an Master of Science in Engineering Management (M.Sc.EM) from Tufts University in Boston MA.

Data centers must minimize downtime and improve operational efficiency while increasing compute intensity using advanced electronics. Latent production defects and aging effects that appear during system operation significantly impact the reliability of data-center electronics and are an important contributor to silent data corruption. This presentation will demonstrate how deep data analytics based on designed-in chip telemetry provide a new way of addressing these challenges in production tests and in the field with real-world use-cases.

A New Way of Measuring Heterogeneous-SoC Performance

Hanan Moller, Technical Director, Siemens

Hanan is the Technical Director, Customer Solutions Architect, responsible for the Applications Engineering team at Tessent Embedded Analytics. Prior to this role, Hanan held various architecture and design roles with BluWireless, Imagination Technologies, Nvidia, ST-Ericsson and Agere Systems. Hanan holds an MSc in Electrical Engineering and a BSc in Computer Engineering from the Technion, Israel Institute of Technology.

While numerous tools exist for measuring heterogeneous-SoC performance at the chip level, it’s more difficult to understand performance at the micro-architecture and system level. This presentation will introduce a measurement methodology that combines debug and monitoring IP with placement heuristics applicable to any IC architecture. It will show how the methodology can improve productivity throughout development, realization and deployment, addressing functional coverage, product qualification, bring-up, software development, defect analysis, and future-chip planning.

Advanced Semiconductor Manufacturing Technologies for Quantum Computing

Anthony Yu, Vice President, Silicon Photonics Product Management, GlobalFoundries

Dr. Anthony J. Yu is Vice President of the Computing and Wired Infrastructure (CWI) Segment Business Unit at GLOBALFOUNDRIES (GF), where he is responsible for providing differentiated photonic manufacturing services and solutions to clients across multiple industries. Prior to being named VP of CWI, Dr. Yu was Vice President of GF’s Aerospace and Defense Business Unit. Before joining GF, he held multiple executive positions at IBM, including Vice President of Semiconductor Technology for Engineering and Technology Services. Yu earned his BS in Physical Chemistry from the University of California-Berkeley and his PhD in Physical Chemistry / Materials Science from Cornell University.

Quantum computing has the potential to solve some of the world's most difficult problems in a broad range of subjects. Bringing this potential to practical reality requires advanced, at-scale manufacturing technologies in the electrical and photonics domains. This presentation will explore the semiconductor-manufacturing advances that will enable mainstream, commercially available quantum computing.

This session will include Q&A after each presentation.

Track B

Session 6: Technologies for Building Heterogeneous Devices Using Chiplets

Breaking a large SoC into smaller physical components—chiplets—has emerged as a technique to overcome challenges associated with SoC development. Most chiplet-based designs have used in-house components, but mixing and matching chiplets from different suppliers opens up new possibilities. Meanwhile, the die-to-die interconnect required for chiplets to communicate is an important technology in every design. This session led by TechInsights Director of Market Analysis Joseph Byrne looks at chiplets and chiplet-interconnect technologies.

Integration of High-Performance FPGA Chiplets in Heterogenous Systems

Nick Ilyadis, Senior Director of Product Planning, Achronix

Nick Ilyadis is the Senior Director of Product Planning at Achronix. With over 35 years of data and semiconductor engineering and manufacturing experience and 72 issued patents under his name, Nick is a recognized expert on software and hardware development and quality control. Prior to joining Achronix, Nick was VP of Portfolio and Technology Strategy at Marvell Semiconductor and Vice President and Group CTO at Broadcom. As the SDPP, Nick oversees all aspects of the Achronix product pipeline, from concept to production.

Heterogenous integration of FPGA-based accelerators with high-performance compute elements has been a much-demanded technology to combat the costs of monolithic solutions. The advent of standardized interfaces has made this possible using chiplets, tiny ICs that contain well-defined functions. FPGAs provide the ideal base to connect chiplets together in one package. This talk will discuss an FPGA architecture that includes a two-dimensional network on chip that interconnects function blocks for transferring data on chip or between dies with low latency and high bandwidth.

Powering the Chiplet Revolution

Elad Alon, CEO and co-founder, Blue Cheetah

Elad Alon is CEO and co-founder at Blue Cheetah. He is an Adjunct Professor of EECS at UC Berkeley and has led many industrial and academic efforts in integrated circuit design and design productivity. He received his Ph.D., M.S., and B.S. degrees from Stanford University and is an IEEE Fellow.

Chiplets offer a cost-effective, agile, and flexible way to build semiconductors. Still, they bring new challenges to the design process. We introduce an IP generator platform that produces state-of-the-art in-package, die-to-die communication solutions that are configurable and process portable. Based on a customer’s specifications for packaging type, data rate, I/O configuration, process, and other high-level parameters, the platform rapidly creates standard-compliant customized tapeout-ready designs with optimized PPA.

Enabling Heterogeneous Integration of Chiplets through Advanced Packaging

Ivor Barber, Corporate Vice President of Packaging, AMD

Ivor Barber is Corporate Vice President of Packaging at AMD developing, advanced package solutions with chiplet architecture in high performance computing, graphics and visualization technologies. With over 40 years of experience in the field of semiconductor packaging Ivor, has held engineering and engineering management positions at National Semiconductor, Fairchild, VLSI Technology, LSI Logic, and Xilinx. Ivor is a frequent panelist and presenter in packaging forums with deep experience in leading edge packaging solutions and high-density interconnect technologies. Ivor has 20 published US patents in semiconductor package manufacturing and package design and is a board member of MEPTEC. Ivor has a Bachelor of Science Degree in Manufacturing Technology from Napier University, Scotland, UK.

To enable heterogeneous Integration of chiplets in a single package or module, advanced packaging techniques are required. The device architect and package designer must co-develop a package solution to achieve the appropriate PPAC (Power, Performance, Area & Cost). Various advanced packaging techniques are discussed including EFB and AMD V-Cache.

There will be Q&A and a panel discussion featuring above speakers.

5:25 – 6:55 PM

Reception and Exhibits – Sponsored by Flex Logix