UltraScale+ Goes Spartan

Author: Dylan McGrath

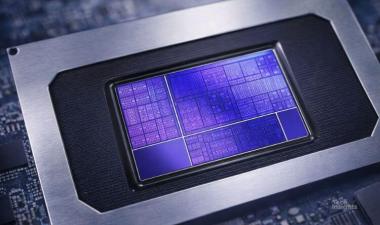

The first new low-cost Spartan FPGAs in the better part of a decade are set to use the UltraScale+ 16-nm architecture that other Xilinx (and AMD) FPGAs and SoCs began migrating to in 2015. Plans call for Spartan UltraScale+ FPGAs to also integrate hard intellectual property (IP) and advanced security features to support a lifecycle of more than 15 years. The devices, which are slated to begin sampling next year, would also offer more than four times the on-chip memory, over 30% more maximum I/O pins, and an increase in power efficiency of up to 30% compared to their predecessors, Spartan 7 FPGAs.

Spartan FPGAs were traditionally offered by Xilinx as the high-volume, low-cost counterpart to the high-performance Virtex FPGA family. Over the years, as the number of FPGA families marketed by Xilinx (now part of AMD) grew, Spartan devices remained true to their roots, offering customers lower capacity but the best bang for the buck in terms of I/Os for everything from glue logic to healthcare, industrial robotics, and edge sensing applications. Spartan UltraScale+ FPGAs further that value proposition, offering up to 572 I/Os, up to 3.35 MB of on-chip memory, and cost-reduction features including the power savings that come with the migration to 16 nm and the inclusion of hard IP blocks.